| Sandy Bridge - новая архитектура процессоров Intel - Усовершенствования конвейера |

| Автор: Grek | ||||||

| 08.01.2011 12:27 | ||||||

Страница 2 из 5

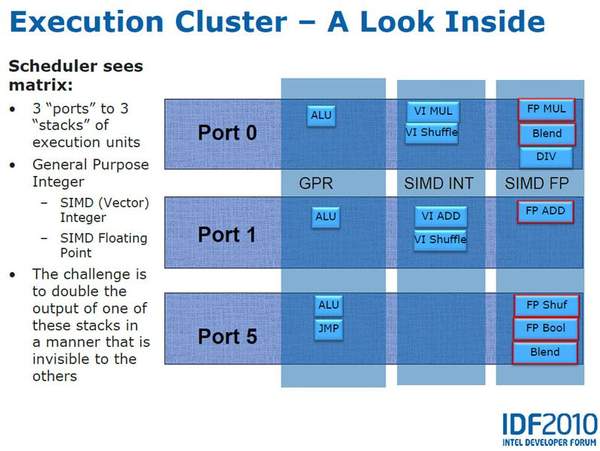

Усовершенствования конвейера CPU Давайте начнем с того, как в микроархитектуре Sandy Bridge обрабатываются инструкции. Для инструкций имеется четыре декодера. Это означает, что CPU может декодировать до четырех инструкций на такт. Декодеры отвечают за преобразование инструкций IA32 (x86) в микрокоманды RISC (µops), которые используются внутренними исполнительными модулями процессора. Как и в предыдущих процессорах Intel, модули декодирования в микроархитектуре Sandy Bridge поддерживают macro-fusion и micro-fusion. Macro-fusion позволяет CPU объединять две инструкции x86 в одну, а micro-fusion позволяет объединять несколько инструкций в ряд микроопераций. Новшеством архитектуры Sandy Bridge стало введение кеша декодируемых микрокоманд, который способен хранить 1536 микрокоманд. Intel назвали этот кеш, как “кэш L0”. Идея здесь очевидна. Если на обработку поступает инструкция, то сначала проверяется кэш L0. В случае совпадения, микрооперации загружаются из кэша L0. В результате отпадает потребность повторно декодировать одни и те же инструкции. Когда нужная инструкция уже декодирована, и находится в кеше, блоки декодирования отключаются. Таким образом, кеш L0 позволяет экономить не только время, но и энергопотребление. Согласно данным Intel, 80% обращений к данному кешу успешны. На первый взгляд данная идея похожа на используемый в микроархитектуре Netburst (Pentium 4) кеш трассировки, который также хранил декодируемые микрокоманды. Но в отличие от кеша микрокоманд он работал по-другому. Кеш трассировки хранил цепочку инструкций в том же порядке, в которым они обрабатывались. Таким образом, среди этих последовательностей инструкций в кеше сохранялись и одинаковые. Этого удалось избежать в кеше L0, который хранит индивидуальные инструкции. Модуль предсказания ветвлений в Sandy Bridge также был усовершенствован по сравнению с предыдущим поколением. Размер Branch Target Buffer (BTB) - буфер с результатами предсказания ветвлений был удвоен по сравнению с архитектурой Nehalem, что является значительным плюсом. Задача блока предсказаний ветвлений заключается в предположении следующих шагов программы и загрузке в CPU нужных инструкций. Если предположение правильно, то работа значительно ускоряется, так как процессору уже не нужно будет тратить время на загрузку данных инструкций из памяти. Планировщик, используемый в микроархитектуре Sandy Bridge, подобен используемому в Nehalem. Он имеет три порта для работы с памятью и три порта, используемые исполнительными блоками. И хотя конфигурации подобны, микроархитектура Sandy Bridge имеет больше исполнительных блоков: 15 против 12 у Nehalem. (см. рисунок ниже). По словам Intel, в результате данных усовершенствований была увеличена скорость выполнения операций с плавающей точкой (то есть, математических операций).

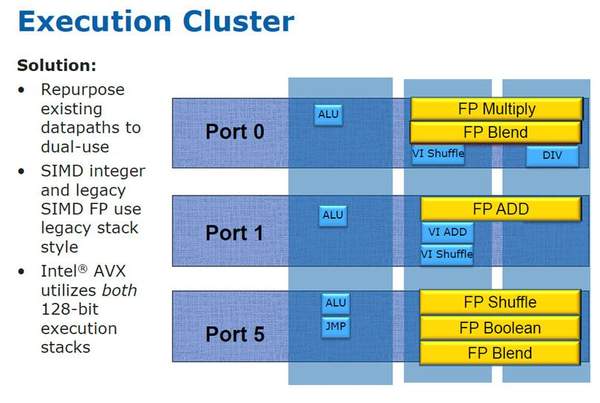

Каждый исполнительный блок соединен с планировщиком 128-битной шиной данных. Для выполнения новых инструкций AVX, которые несут 256-битные микрокоманды, одновременно используются два исполнительных блока. Как это происходит схематично показано на рисунке ниже.

После того, как инструкция выполнена, она не копируется назад в буфер, как это было в предыдущей архитектуре Intel, а отмечается выполненной. Таким образом, повышается эффективность CPU. Также различия есть и в работе портов с памятью. Также как в архитектуре Nehalem реализованы три порта для работы с памятью, но два порта, которые раньше сохраняли адреса и загружали данные, теперь могут загружать адреса и данные или выгружать адреса. Третий порт так и остался для сохранения данных. В результате данного изменения пропускная способность кеша выросла на 50%. Теперь за один такт процессор загружает 32 байт и сохраняет 16 байт данных.

Понравилась новость? Поделись с друзьями! |

||||||

| Обновлено 29.09.2014 14:20 |

Разное

Заметили ошибку в тексте?

Сообщите админу - выделите текст с ошибкой и нажмите Shift+Enter.

Спасибо!

Подписка на новости сайта

Авторизация

Последние статьи

Штатив Rekam Ecopod E-156

13 Апр 2017 Прочее железо Hits:6400 Комментарии

Обзор портативного жесткого диска Verbatim Store ‘n’ Go 1 Тб USB 3.0

28 Авг 2016 Прочее железо Hits:6569 Комментарии

Характеристики, производительность и цена NVIDIA GeForce 740

24 Май 2016 Видеокарты Hits:5830 Комментарии

Характеристики, обзор и цена NVIDIA GeForce GTX 745

25 Фев 2016 Видеокарты Hits:12275 Комментарии

Характеристики, обзор и цена NVIDIA GeForse 8500 GT

22 Фев 2016 Видеокарты Hits:8262 Комментарии

Популярные статьи

Обзор ноутбука Lenovo G560

26 Сен 2010 Ноутбуки Hits:30602 Комментарии

Обзор видеокарты Sapphire Radeon HD 5830 1Гб GDDR5

06 Мар 2010 Видеокарты Hits:27900 Комментарии

Установка Windows XP на ноутбук Acer Aspire 5315

20 Фев 2010 Ноутбуки Hits:25933 Комментарии

Установка Windows XP на ноутбук Samsung R560

10 Апр 2010 Ноутбуки Hits:23871 Комментарии

Обзор ноутбука ASUS UL20FT

03 Сен 2010 Ноутбуки Hits:22652 Комментарии