| Sandy Bridge - новая архитектура процессоров Intel - Кольцевая шина |

| Автор: Grek | ||||||

| 08.01.2011 12:27 | ||||||

Страница 3 из 5

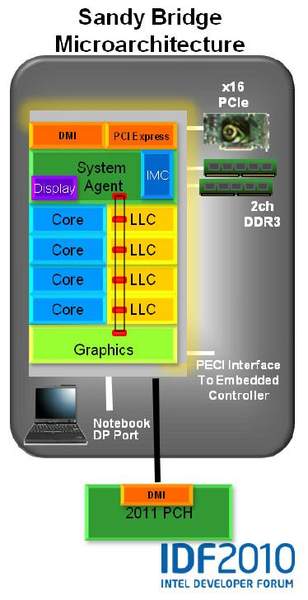

Инструкции AVX Совсем недавно компания AMD предложила систему команд SSE5. Однако Intel решили создать свою собственную реализацию SSE5, которая получила название AVX (Advanced Vector Extensions). Данные инструкции представляют собой дальнейшее развитие SSE и используют те же операции SIMD (Single Instruction, Multiple Data), ведущих свое начало с системы команд MMX. Только в AVX для ускорения обработки данных увеличена разрядность операций. Система команд AVX добавляет 12 новых инструкций и увеличивает размер регистров XMM со 128 бит до 256 бит. Кольцевая шина Для обмена данными между внутренними компонентами CPU в архитектуре Sandy Bridge предусмотрена кольцевая шина. Упрощенно ее можно описать следующим образом. Когда компонент хочет "общаться" с другим компонентом, он помещает информацию в кольцевую шину, а она перемещает эту информацию адресату. Компоненты не "говорят" непосредственно друг с другом, они должны использовать кольцо. Кольцевая шина используется для общения между ключевыми компонентами процессора. Это ядра CPU, кэш-память L3 (теперь называется кеш-память последнего уровня или LLC), а также System Agent (в него входят интегрированный контроллер памяти, контроллер PCI Express, блок управления питанием и дисплей) и графическое ядро. На рисунке ниже Вы можете видеть схему кольцевой шины (черный овал) с ее "остановками" (красные прямоугольники). Доступ к кешу L3 имеют не только процессорные ядра, но также графическое ядро и system agent. Каждое процессорное ядро имеет прямой доступ к своему сегменту кеша L3. Все сегменты кеша L3 имеют контроллер доступа к кольцевой шине. Кроме того, ядра CPU не привязаны в определенному сегменту кеша. Любое ядро может использовать любой из кешей. На рисунке ниже изображен четырехъядерный CPU с четырьмя сегментами L3. Так, например, Core 1 может обращаться не только к кешу 1, а к любому. То есть любое ядро процессора может получить доступ данным, которые хранятся в любом из кешей.

Кольцевая шина включает фактически четыре 32-х байт колец: шина данных (Data Ring), шина запросов (Request Ring), шина подтверждения (Acknowledge Ring) и шина мониторинга (Snoop Ring). Все они работают на тактовой частоте процессора. Передача данных между ними основана на протоколе QPI (QuickPath Interconnect), который используется в CPU LGA 1366 для обмена данными с чипсетом. Каждый компонент решает, нужно ли ему использовать кольцевую шину, если она свободна. Кольцо всегда выбирает кратчайший путь к месту назначения.

Понравилась новость? Поделись с друзьями! |

||||||

| Обновлено 29.09.2014 14:20 |

Разное

Заметили ошибку в тексте?

Сообщите админу - выделите текст с ошибкой и нажмите Shift+Enter.

Спасибо!

Подписка на новости сайта

Авторизация

Последние статьи

Штатив Rekam Ecopod E-156

13 Апр 2017 Прочее железо Hits:6401 Комментарии

Обзор портативного жесткого диска Verbatim Store ‘n’ Go 1 Тб USB 3.0

28 Авг 2016 Прочее железо Hits:6570 Комментарии

Характеристики, производительность и цена NVIDIA GeForce 740

24 Май 2016 Видеокарты Hits:5831 Комментарии

Характеристики, обзор и цена NVIDIA GeForce GTX 745

25 Фев 2016 Видеокарты Hits:12275 Комментарии

Характеристики, обзор и цена NVIDIA GeForse 8500 GT

22 Фев 2016 Видеокарты Hits:8262 Комментарии

Популярные статьи

Обзор ноутбука Lenovo G560

26 Сен 2010 Ноутбуки Hits:30602 Комментарии

Обзор видеокарты Sapphire Radeon HD 5830 1Гб GDDR5

06 Мар 2010 Видеокарты Hits:27901 Комментарии

Установка Windows XP на ноутбук Acer Aspire 5315

20 Фев 2010 Ноутбуки Hits:25934 Комментарии

Установка Windows XP на ноутбук Samsung R560

10 Апр 2010 Ноутбуки Hits:23872 Комментарии

Обзор ноутбука ASUS UL20FT

03 Сен 2010 Ноутбуки Hits:22652 Комментарии